DESIGN FOR TESTABILITY ENGINEER RESUME EXAMPLE

Updated: Mar 19, 2025 - The Design for Testability Engineer oversees technology management in projects, offering technical guidance and solutions to ensure efficient work completion. Responsible for developing and mentoring team members, the role focuses on enhancing technical capabilities and increasing productivity. Involves implementing DFT flows for complex ASICs, using advanced EDA tools like Mentor Tessent and Cadence, and executing DFT insertion, ATPG, and pattern simulation for current designs.

Tips for Design for Testability Engineer Skills and Responsibilities on a Resume

1. Design for Testability Engineer, MicroLogic Systems, Austin, TX

Job Summary:

- Completing all required safety training and conducting all work in accordance with Micron safety policies

- Developing new product test methods and strategies

- Owning and driving the product test release roadmap

- Coordinating and communicating product test releases across teams

- Calibration and validation of product test limits

- Analyzing the results of experimental product test changes

- Analyzing a wide variety of research, product, and manufacturing data

- Developing and implementing device algorithm and trim by die optimizations

- Assisting in electrical characterization through device schematic and failure model hypotheses

- Partnering with other stakeholders to discover previously unknown device failure modes

Skills on Resume:

- Safety Training (Hard Skills)

- Test Methodology (Hard Skills)

- Roadmap Management (Hard Skills)

- Team Coordination (Soft Skills)

- Calibration Expertise (Hard Skills)

- Data Analysis (Hard Skills)

- Electrical Characterization (Hard Skills)

- Problem Solving (Soft Skills)

2. Design for Testability Engineer, NexGen Semiconductors, Fremont, CA

Job Summary:

- Develop and implement DFT and ATPG flow

- Participate in development and implementation of DFT architecture with design team

- Work with the DFT and Synthesis CAD team to verify DFT implementations

- Support tool and infrastructure to generate structural test vectors , analyzing and improving coverage

- Work with DFT designers on STA, physical, power and logical issues

- Drive DFT and ATPG vendor engagements

- Performing electrical failure debug and device function validation through bench analysis in lab environment

- Performing electrical bench/lab tests to validate the safety, quality, and effectiveness of proposed product test changes

- Developing and implementing test time reductions to reduce test and production costs

- Communicating highly technical concepts to engineers of various backgrounds

- Reporting progress and risks to leadership in a timely manner

Skills on Resume:

- DFT Implementation (Hard Skills)

- ATPG Development (Hard Skills)

- CAD Collaboration (Hard Skills)

- Test Vector Analysis (Hard Skills)

- DFT Design Support (Hard Skills)

- Vendor Management (Soft Skills)

- Bench Testing (Hard Skills)

- Technical Communication (Soft Skills)

3. Design for Testability Engineer, Quantum Circuits Solutions, Raleigh, NC

Job Summary:

- Managing technology in projects and providing technical guidance or solutions for work completion

- Providing technical guidance or solutions

- Develop and guide the team members in enhancing their technical capabilities and increasing productivity

- Prepare and submit status reports for minimizing exposure and risks on the project or closure of escalations.

- Ensure process compliance in the assigned module, and participate in technical discussions or review.

- Develop understanding of both the block level and chip top DFT / ATPG / Test flow s for complex ASICs

- Develop and prototype new DFT flows using Mentor Tessent or Cadence EDA tools

- Complete DFT insertion, ATPG, and pattern simulation steps for current designs.

Skills on Resume:

- Technology Management (Soft Skills)

- Technical Guidance (Soft Skills)

- Team Development (Soft Skills)

- Risk Management (Soft Skills)

- Process Compliance (Soft Skills)

- ASIC Understanding (Hard Skills)

- DFT Prototyping (Hard Skills)

- ATPG Implementation (Hard Skills)

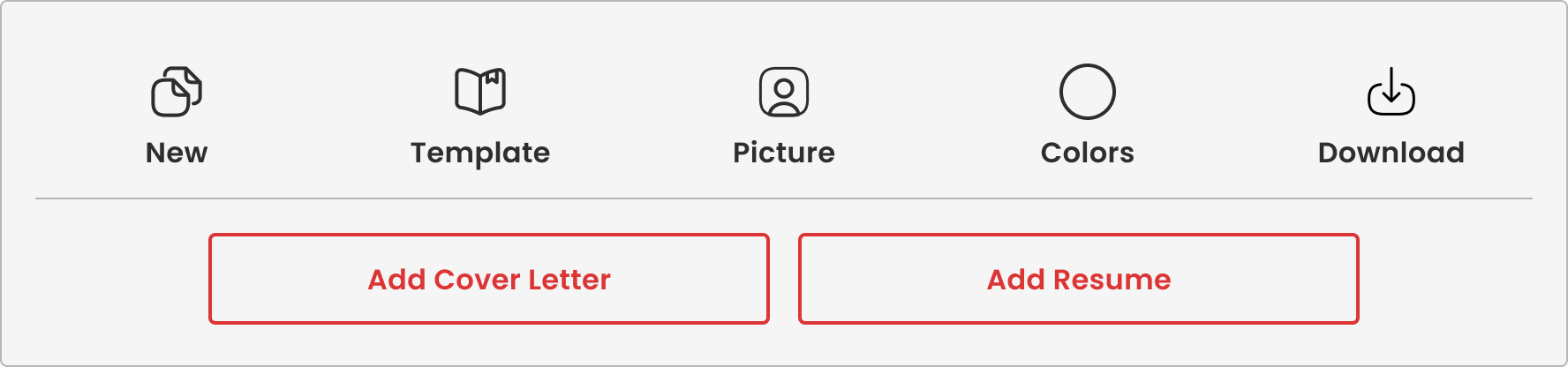

Resume Standards 2026

Lamwork's key guidelines and best practices for writing a professional, ATS-friendly resume.

1. Contact Information

Name, phone number, professional email, LinkedIn, portfolio (if applicable)

2. Professional Summary (2-3 lines)

Role + years of experience + key strengths

3. Work Experience

Title + company + dates

Bullet points: action verbs + metrics + impact

Add context (what/why) when needed

Not recommended: Increased sales by 20%

Recommended: Increased B2B sales by 20% by optimizing outreach strategy

4. Skills

Hard skills only + match job description keywords (ATS)

5. Education

Degree, school, year (GPA if strong)

6. Projects (if relevant)

Name + tools + outcomes

7. Format

0-5 years: 1 page

5-10 years: up to 2 pages

Clean font, no photo, no personal details

8. ATS Optimization

Use exact keywords from the job description

Avoid tables or columns

Example:

Job says "Data Analysis" -> use "Data Analysis"

Do not change it to "Analyzing Data"

9. Do Not Include

Photo, age, gender, full address, references

10. Final Check

No typos, consistent verb tense, tailored for each job

File name: FirstName_LastName_Resume.pdf

Editorial Process and Content Quality

This content is part of Lamwork's career intelligence platform and is developed using structured analysis of real-world job data, including publicly available job descriptions, skill requirements, and hiring patterns.

Lam Nguyen, Founder & Editorial Lead, defines the research framework behind Lamwork's career intelligence platform, including job role analysis, skills taxonomy, and structured career insights.

All content is reviewed by Thanh Huyen, Managing Editor, who oversees editorial quality, content consistency, and alignment with real-world role expectations and Lamwork's editorial standards.

Content is developed through a structured process that includes data analysis, role and skill mapping, standardized content formatting, editorial review, and periodic updates.

Content is reviewed and updated periodically to reflect changes in skills, role requirements, and labor market trends.

Learn more about our editorial standards.